Cache-Oblivious Algorithmus

Ein cache-oblivious Algorithmus ist ein Algorithmus, der effizient auf Architekturen mit mehrstufiger Speicherhierarchie arbeitet, ohne deren genaue Parameter zu kennen. Diese Parameter sind zum Beispiel die Anzahl der Caches, die Größe der jeweiligen Cachezeilen oder deren Zugriffszeiten. Die Performance wird im sogenannten Idealized Cache Modell analysiert, in dem das Kostenmaß die Cache-Misses sind. Ein cache-oblivious Algorithmus ist optimal, wenn er die Caches asymptotisch optimal benutzt, also eine bis auf konstante Faktoren minimale Anzahl an Cache-Misses erzeugt.

Entwurfsziel ist eine gute Performance des gleichen Codes auf verschiedenen Maschinen mit vielen Speicherebenen, ohne dass Anpassungen an die Architektur gemacht werden müssen. (Für eine optimale Performance müssen allerdings noch Anpassungen an die jeweilige Hardware vorgenommen werden, die über die Speicherhierarchie hinausgehen.)

Cache-oblivious Algorithmen sind verwandt mit External Memory Algorithmen, bei denen im Gegensatz aber nur von einer zweistufigen Speicherhierarchie ausgegangen wird und bei denen die Größe des kleineren/schnelleren sowie die Blockgröße des größeren/langsameren Speichers dem Algorithmus als Eingabeparameter zur Verfügung stehen. Ein optimaler cache-oblivious Algorithmus für zwei Speicherebenen ist auch optimal für beliebig viele Speicherebenen[1].

Geschichte[Bearbeiten | Quelltext bearbeiten]

Die erste Idee (und der Name) zu cache-oblivious Algorithmen stammt von Charles E. Leiserson aus dem Jahr 1996, die erste Veröffentlichung dazu ist die Masterarbeit von Harald Prokop am Massachusetts Institute of Technology von 1999[1]. Dort werden bereits cache-oblivious Algorithmen zur Matrixtransposition, für die Schnelle Fourier-Transformation und fürs Sortieren vorgestellt.

Bereits vorher wurde eine Vielzahl von Algorithmen entwickelt, die als cache-aware bezeichnet werden können. Diese arbeiten ebenfalls optimal mit dem vorhandenen Caches, müssen dafür aber deren Parameter (Größe, Zeilenlänge) kennen.

Analyse im Idealized Cache Modell[Bearbeiten | Quelltext bearbeiten]

Cache-oblivious Algorithmen werden im Idealized Cache Modell (alternativ Cache Oblivious Modell) analysiert[2]. Es basiert auf dem RAM-Modell. Der Prozessor arbeitet mit einer konstanten Anzahl an Registern auf einem unendlichen Hauptspeicher, in dem auf jede Speicherzelle in zugegriffen werden kann. Als Erweiterung wird nun eine zweite Speicherebene, der Cache, zwischen Prozessor und Hauptspeicher eingefügt. Die weiteren Unterschiede im Idealized Cache Modell sind:

- Der Hauptspeicher ist unterteilt in Blöcke der Größe .

- Der Cache kann Speicherworte enthalten. Dabei wird angenommen (sog. tall cache assumption).

- Eine Lese-/Schreiboperation zwischen Prozessor und Hauptspeicher kann nun durch den Cache erledigt werden. Falls dies nicht möglich ist, spricht man von einem Cache-Miss.

- Bei einem Cache-Miss: Soll auf ein Speicherwort zugegriffen werden, das in einem Block des Hauptspeichers liegt, wird der ganze Block in den Cache geladen. Sollte der Cache bereits voll sein, muss vorher ein anderer Block verdrängt, also aus dem Cache zurück in den Hauptspeicher geschrieben werden.

- Der Cache hat volle Assoziativität, das heißt, dass jeder Speicherblock an jede Position des Caches geladen werden kann.[3]

- Die Verdrängungsstrategie ist optimal. Es wird also angenommen, dass der Cache die genaue Reihenfolge aller (auch der zukünftigen) Speicherzugriffe kennt und immer den Block aus dem Cache verdrängt, auf den erst am weitesten in der Zukunft wieder zugegriffen wird. Dies ist natürlich eine unrealistische Annahme, aber eine LRU Strategie approximiert dies bis auf einen kleinen konstanten Faktor[4][5].

Die Parameter und sind dem Algorithmus dabei nicht bekannt.

Zum Analysieren der Komplexität eines Algorithmus im Idealized Cache Modell werden nur die Cache-Misses gezählt. Dies wird durch die sehr großen Unterschiede in der Zugriffszeit zwischen den verschiedenen Speicherebenen gerechtfertigt. Dabei werden die Unterschiede mit steigender Speicherkapazität immer extremer: Beispielsweise kann auf ein Register in einem Taktzyklus zugegriffen werden, ein Zugriff auf einen Wert in einem Cache benötigt bereits wenige Nanosekunden und ein Arbeitsspeicherzugriff dauert ca. 60–70 Nanosekunden. Noch extremer sind die Unterschiede bei Massenspeichermedien und Wechseldatenträgern, wo die Zugriffszeiten im Bereich von Millisekunden (bei Festplatten) bis Minuten (CDs, Magnetbänder) liegen können.

Beziehung zum External Memory Modell und zur Realität[Bearbeiten | Quelltext bearbeiten]

Im External Memory Modell werden dem Algorithmus die Parameter und als Teil der Eingabe übergeben und es macht keine Vorgaben über die Verdrängungsstrategie des Caches. Dadurch kann der Algorithmus die vorhandene Hardware noch um einen konstanten Faktor effizienter nutzen. Die Analyse im External Memory Modell ist sehr ähnlich, hier werden nur die Zugriffe auf den externen Speicher gezählt werden. Der Vorteil eines effizienten Algorithmus im Idealized Cache Modell ist, dass der gleiche Algorithmus auch auf Maschinen mit anderen und effizient ist. Genauso ergibt sich eine Effizienz über mehrere Speicherebenen, bei denen sich die Parameter und zwischen verschiedenen Ebenen zum Teil um Größenordnungen unterscheiden.

Das Modell eines idealen Caches ist deutlich einfacher als ein realer Cache. Gerade schnelle Caches (z. B. L1-Caches) haben für bessere Performance in der Regel keine vollständige Assoziativität. Außerdem existiert eine optimale Verdrängungsstrategie nur in der Theorie und muss in der Praxis approximiert werden. Die sich dadurch ergebenen Laufzeitunterschiede lassen sich in vielen Fällen jedoch beweisbar durch kleine konstante Faktoren einschränken[4].

Beispiele[Bearbeiten | Quelltext bearbeiten]

Viele cache-oblivious Algorithmen arbeiten nach dem Teile und Herrsche Prinzip, bei dem das Problem so weit in kleinere Instanzen aufgeteilt wird, dass die einzelnen Teilprobleme in den Cache passen. Diese können dann effizient gelöst und in einem cache-effizienten Verfahren wieder zu einer Lösung der ursprünglichen Instanz zusammengesetzt werden. Auch bei den beiden folgenden Algorithmen wird dieses Prinzip angewendet.

Matrixtransposition[Bearbeiten | Quelltext bearbeiten]

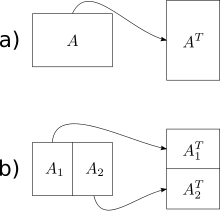

Als erstes Beispiel soll hier ein cache-oblivious Algorithmus zur Transposition einer rechteckigen Matrix vorgestellt werden, der auf Harald Prokop zurückgeht[1]. Dabei steht die Eingabe in einer -Matrix und die Ausgabe soll in eine -Matrix geschrieben werden. Eine naive Lösung durchläuft zeilenweise und spaltenweise und kopiert in jedem Schritt einen Wert von nach . Sind die Matrizen hinreichend groß, führt jeder Zugriff der spaltenweise durchlaufenen Matrix zu einem Cache-Miss. Damit ergibt sich eine Gesamtarbeit von und Cache-Komplexität von . Der cache-oblivious Algorithmus nutzt aus, dass das Transponieren der gesamten Matrix in das Transponieren von zwei Teilmatrizen aufgeteilt werden kann. Dazu wird die Matrix entlang der größeren Dimension in zwei (annähernd) gleich große Teilmatrizen geteilt, bis die einzelnen Teile der Größe doppelt in den Cache passen (als Eingabe- und Ausgabeteilmatrix). Dann kann die Teilmatrix nach dem naiven Verfahren mit Arbeit und Cache-Komplexität transponiert werden. Insgesamt ergibt sich eine optimale Arbeit von und Cache-Komplexität . Theoretisch könnten die Teilmatrizen bis zu einer Größe von weiter zerteilt werden, in der Praxis sollte allerdings ein größerer Basisfall gewählt werden, da selbst kleinste Caches mehr als zwei Speicherworte groß sind und der Zusatzaufwand zum Zerteilen die Cacheeffekte in dieser Größenordnung dominiert.

Sortieren[Bearbeiten | Quelltext bearbeiten]

Als weiteres Beispiel soll ein optimaler cache-oblivious Algorithmus zum Sortieren vorgestellt werden. Harald Prokop hat in seiner Masterarbeit zwei solche vorgestellt: Distribution Sort (basierend auf Quicksort) und Funnelsort[1]. Letzterer basiert auf Mergesort und soll hier beschrieben werden:

Funnelsort sortiert ein Array mit Einträgen rekursiv in zwei Schritten:

- Zerteile das Array in Teilarrays, von denen jedes Größe hat. Sortiere die Teilarrays rekursiv.

- Verschmelze (engl. merge) die sortierten Teilarrays mit einem -Merger.

Die gesamte Komplexität liegt also in dem Merger, der auch Funnel genannt wird. Ein -Merger erhält sortierte Folgen als Eingabe und gibt bei jedem Aufruf die nächsten Elemente der sortierten Folge aus, die aus der Verschmelzung der Eingabefolgen entsteht. Im Unterschied zu Mergesort wird bei Funnelsort auch das Mergen rekursiv gemacht. Diese rekursive Zerlegung der Merge-Operation führt dazu, dass die einzelnen Teilprobleme irgendwann in den Cache passen.

Ein -Merger ist rekursiv aus mehreren -Mergern zusammengesetzt (die Abbildung rechts zeigt einen 9-Merger): Es gibt insgesamt Eingabemerger , auf die die Eingaben gleichmäßig verteilt werden. Jeder Eingabemerger schreibt seine Ausgabe in einen eigenen Puffer der Größe . Dazu gibt es einen Ausgabemerger , dessen Eingänge mit den Puffern von verbunden sind und dessen Ausgabe auch die Ausgabe des -Mergers ist. Jeder der verbauten -Merger hat Eingaben und produziert eine Ausgabe von Elementen.

Bei einem Aufruf des -Mergers müssen nun Elemente ausgegeben werden. Dazu wird der Ausgabemerger insgesamt -mal aufgerufen, der dabei in jedem Aufruf weitere Elemente ausgibt. Vor jedem Aufruf wird dabei sichergestellt, dass jeder Puffer in der Eingabe von mindestens Elemente enthält. Sollte dies bei Puffer nicht der Fall sein, wird zuerst Eingabemerger aufgerufen, der neue Elemente in den Puffer schreibt. Die Größe des Puffers wurde dabei gerade so gewählt, dass immer ausreichend Platz vorhanden ist.

Brodal und Fagerberg beschreiben darüber hinaus eine Variante Lazy Funnelsort[6], in der ein Puffer erst dann neu befüllt wird, wenn er vollständig leer ist. Dies kann in der Praxis etwas schneller sein. Die Autoren beweisen dazu, dass es in der Theorie zur gleichen Anzahl Cache Misses kommt.

Siehe auch[Bearbeiten | Quelltext bearbeiten]

Einzelnachweise[Bearbeiten | Quelltext bearbeiten]

- ↑ a b c d Harald Prokop. Cache-Oblivious Algorithms. Masters thesis, MIT. 1999.

- ↑ Erik D. Demaine: Cache-Oblivious Algorithms and Data Structures. In: MIT Laboratory for Computer Science. 2000 (erikdemaine.org [PDF]).

- ↑ Piyush Kumar: Cache-Oblivious Algorithms. In: Algorithms for Memory Hierarchies. Springer Verlag, S. 193–212 (citeseerx.ist.psu.edu ( des vom 11. Juli 2012 im Internet Archive)).

- ↑ a b M. Frigo, C. E. Leiserson, H. Prokop, S. Ramachandran: Cache-oblivious algorithms. Proc. IEEE Symp. on Foundations of Computer Science (FOCS). 1999, S. 285–297 (englisch, mit.edu [PDF]).

- ↑ Daniel Sleator, Robert Tarjan. Amortized Efficiency of List Update and Paging Rules. In Communications of the ACM, Volume 28, Number 2, p.202–208. Feb 1985.

- ↑ Gerth Brodal, Rolf Fagerberg: Cache Oblivious Distribution Sweeping. In: Proceedings of the 29th International Colloquium on Automata, Languages, and Programming. 2380 of Lectrue Notes in Computer Science. Springer Verlag, S. 426–438.