Standardzelle

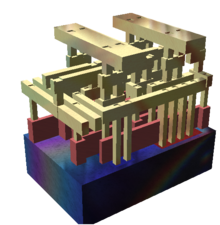

Standardzelle steht im mikroelektronischen Entwurf für eine festgelegte Implementierung eines Logikgatters, das für den Einsatz in komplexen digitalen Schaltungen konzipiert wurde.

Bei Standardzellen steht das Layout des Einzelgatters vor Entwurfsbeginn bereits fest. Der Entwurf mit Standardzellen vermindert das Risiko von Fehlfunktionen, da sich der Verifikationsaufwand für eine damit entworfene Schaltung drastisch reduzieren lässt. Im Gegensatz dazu kann beim manuellen Layout größerer Digitalschaltungen die Gesamtfläche zusätzlich minimiert werden.

Standardzellen werden spezifisch für einen Herstellungsprozess entworfen und bereits vor dem Anlauf der Massenfertigung mit geeigneten Teststrukturen gemessen und charakterisiert. Damit werden die kompletten Schaltungseigenschaften über den geplanten Betriebsbereich (Spannung, Temperatur) erfasst und in entsprechende Simulationsmodelle umgesetzt.

Die Komplexität von Standardzellen reicht von einfachsten Zellen (Inverter aus zwei Transistoren) typisch bis zum Flipflop (bis zu ca. 25 Transistoren).